F40P

IP66 Air Borne Mission Computer

- IP66 Military Air Borne Mission Computer

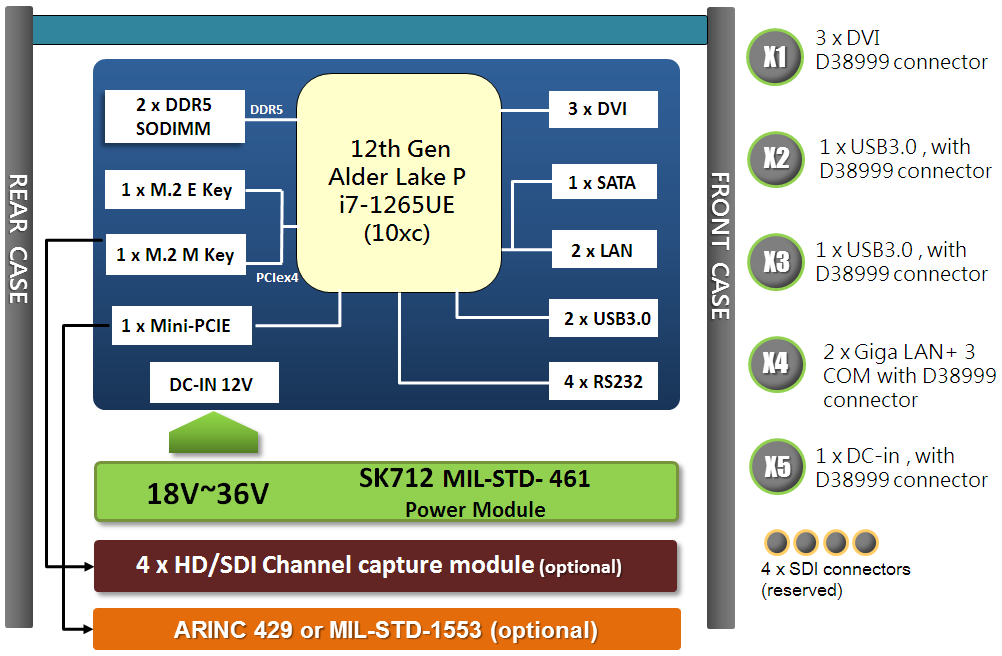

- Intel 12th Gen Alder Lake P, i7-1265UE, 10C, 4.7GHz

- Frame Grabber : 4x CH HD-SDI

- 3x DVI, 2x LAN, 2x USB3.0, 3x COM

- 1x 2.5” Swappable SATA Drive

- MIL-STD 18V~36V EMI DC-IN, Options for MIL-STD-704/ 461/ 1275 10V~40V DC

- Extreme Temperature -40°C to 60°C

- MIL-STD 810 509 Salt Fog (Conformal Coating)

- MIL-STD 810 500.5 Low Pressure (50,000 ft) Altitude

Special Request :

- Frame Grabber : 4x CH HD-SDI

- Discrete IO : 4x DI/4x DO

- MIL-1553 , ARINC 429

- Technical Profile

- Specifications

- Download

- Introduction

-

ATR (Air Transport Rack) is a standard that specifies form fit and function of enclosures designed to protect the main internal system. This military enclosure must meet EMI / EMC requirements to prevent noise interference, provide lightning protection and be isolated from small particle contaminants. So, it can be deployed in unmanned aerial vehicles, fighters, and helicopters. To satisfy diverse conditions, ATR chassis are available in different sizes—1/2, 3/4 and Full ATR sizes. Based on 1/2 ATR size, 7Starlake launches a new Rugged Airborne Mission Computer F40.

- ARINC 429

-

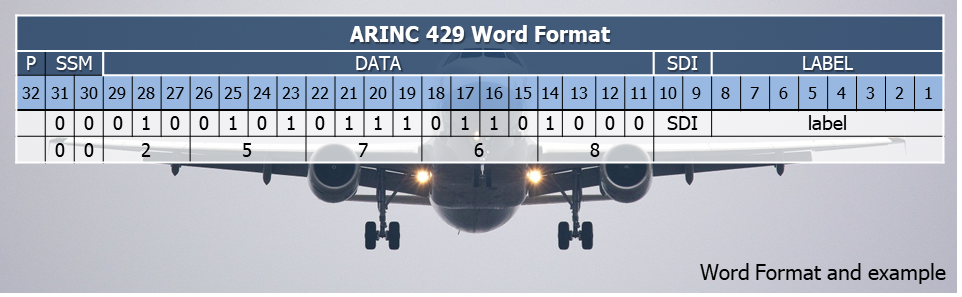

ARINC 429 is the worldwide standard for data transmission in aircraft electronics. It is adopted mostly for commercial aircraft and transport aircraft network protocol standard. Communications, guidance, altitude, altitude reference, flight management, and more are all needed to work together to accomplish a successful flight. The physical connection wires are twisted pairs carrying balanced differential signaling.

The ARINC 429 unit of transmission is a fixed-length 32-bit frame, which the standard refers to as a 'word'. The bits within an ARINC 429 word are serially identified from Bit Number 1 to Bit Number or simply Bit 1 to Bit 32.

- MIL-STD-1553

-

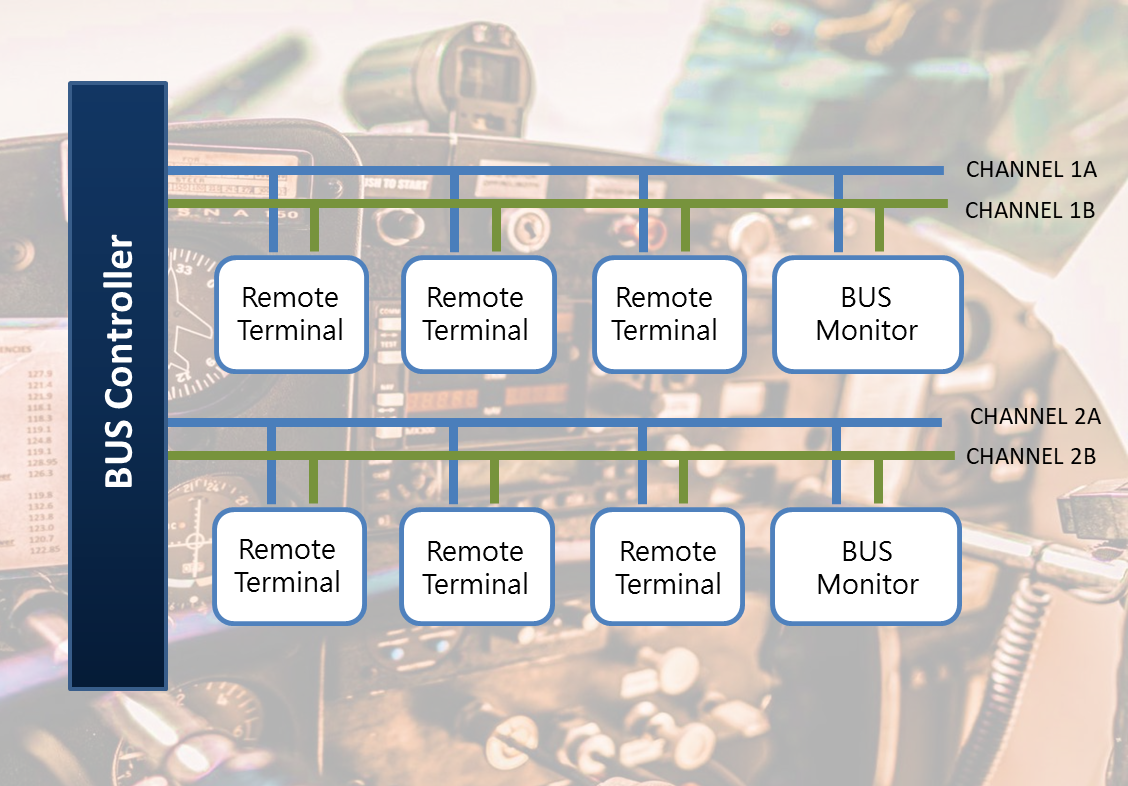

MIL STD 1553 is US Military Department of Defence standard that was initially published in 1973.

MIL STD 1553 is a differential serial bus. Also, it is a dual redundant data bus. Each node is connected to each of the redundant buses. Secondly, if one should fail, communications can still continue.

There are three types of operating nodes for 1553 Bus:

•A Bus Controller initiates all messages, traffic and commands the remote terminals to transmit/receive data.•Remote Terminal interfaces the 1553 Bus and Sub System Bridge to other 1553 Buses. It responds to the bus controller.•The Bus Monitor listens to messages and records them.

- IT Block Diagram

- Features

-

Computing Features

- Core i7-1265UE (up to 4.7 GHz), 15W

- Memory support up to DDR5-64GB

- IP65 Chassis with D38999 connectors

- High performance with lower power efficiency

- 1 x M.2 E Key, 1 x M.2 M Key, 1 x Full Size Mini PCIe

- Appearance & Dimension

-

|

System |

|

|---|---|

|

High Power Processor |

Intel 12th Gen Alder Lake P, i7-1265UE(10xC),4.7GHz |

|

Memory type |

2x DDR5 SODIMM up to 64GB |

|

Chipset |

Intel® SoC Integrated |

|

Graphic |

Intel® Iris Xe Graphics |

|

BIOS |

AMI UEFI BIOS |

|

TPM |

Nuvoton NPCT750AABYXTPM2.0 |

|

Power Type |

18V~36V EMI DC-IN, Options for 10V ~ 36V DC-IN |

|

Storage |

1x 2.5” Swappable SATA SSD Tray |

|

Operating Temperature |

-40° to +60° C |

|

Dimension |

134.36(W) x 177(L)x 287(H) mm |

|

FRONT I/O |

|

|

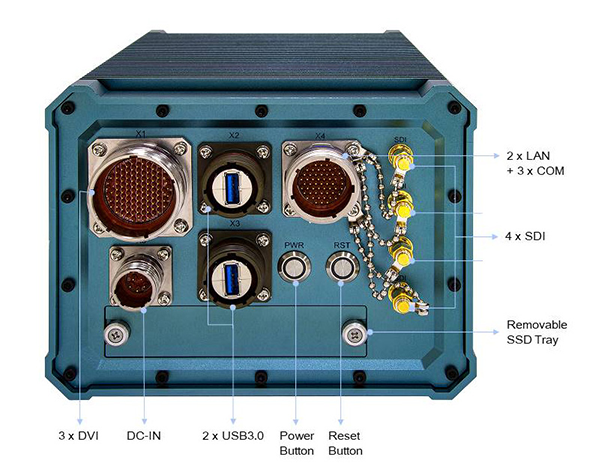

X1 |

3x DVI with 100 PIN D38999 connector |

|

X2 |

1x USB3.0 with USB3.0 D38999 connector |

|

X3 |

1x USB3.0 with USB3.0 D38999 connector |

|

X4 |

2x LAN + 3x COM with 50PIN D38999 connector |

|

X5 |

1x DC in with D38999 connector |

|

others |

1x 2.5” Easy swap HDD/SSD Tray 4x SDI connectors 1x Power button 1x Reset button |

|

Environmental |

|

|

MIL-STD-810 Test

|

Method 500.5, Procedures I and II (Altitude, Operation): 12,192M, (40,000 ft) for the initial cabin altitude (18.8Kpa or 2.73 Psia) Method 500.5, Procedures III and IV (Altitude, Non-Operation): 15,240, (50,000 ft) for the initial cabin altitude (14.9Kpa or 2.16 Psia) Method 501.5, Procedure I (Storage/High Temperature) Method 501.5, Procedure II (Operation/High Temperature) Method 502.5, Procedure I (Storage/Low Temperature) Method 502.5, Procedure II (Operation/Low Temperature) Method 503.5, Procedure I (Temperature shock) Method 507.5, Procedure II (Temperature & Humidity) Method 514.6, Vibration Category 24/Non-Operating (Category 20 & 24,Vibration) Method 514.6, Vibration Category 20/Operating (Category 20 & 24,Vibration) Method 516.6, Shock-Procedure V Non-Operating (Mechanical Shock) Method 516.6, Shock-Procedure I Operating (Mechanical Shock) |

|

Reliability |

No Moving Parts; Passive Cooling. Designed & Manufactured using ISO 9001 Certified Quality Program. |

| MIL-STD-461 |

CE102 basic curve, 10kHz - 30 MHz RE102-4, (1.5 MHz) -30 MHz - 5 GHz RS103, 200 MHz - 3.2 GHz, 50 V/m equal for all frequencies EN 61000-4-2: Air discharge: 8 kV, Contact discharge: 6kV EN 61000-4-3: 10V/m EN 61000-4-4: Signal and DC-Net: 1 kV EN 61000-4-5: Leads vs. ground potential 1kV, Signal und DC-Net: 0.5 kV CE and FCC |

| MIL-STD-1275 |

Steady State – 20V~33V, Surge Low – 18V/500ms, Surge High – 100V/500ms Emitted spikes Injected Voltage surges Emitted voltage surges Voltage ripple (2V) Voltage spikes Starting Operation Reverse polarity |

| MIL-STD-704 |

Load Measurements (LDC101) Steady State Limits for Voltage (LDC102) Voltage Distortion Spectrum (LDC103) Total Ripple (LDC104) Normal Voltage Transients (LDC105) Power Interrupt (LDC201) Abnormal Steady State Limits for Voltage (LDC301) Abnormal Voltage Transients (LDC302) Emergency Steady State Limits for Voltage (LDC401) Starting Voltage Transients (LDC501) Power Failure (LDC601) Phase Reversal (LDC602) |

| Attachment | Size |

|---|---|

| US20160231790A1 - PCI-104_0_0_0.pdf (1.14 MB) | 1.14 MB |